# SNR characteristics of 850-nm OEIC receiver with a silicon avalanche photodetector

Jin-Sung Youn,<sup>1</sup> Myung-Jae Lee,<sup>1</sup> Kang-Yeob Park,<sup>1</sup> Holger Rücker,<sup>2</sup> and Woo-Young Choi<sup>1,\*</sup>

<sup>1</sup>Department of Electrical and Electronic Engineering, Yonsei University, 50 Yonsei-ro, Seodaemoon-gu, Seoul, 120-749, South Korea <sup>2</sup>lm Technologiepark 25, IHP, 15236 Frankfurt (Oder), Germany

\*wchoi@yonsei.ac.kr

**Abstract:** We investigate signal-to-noise ratio (SNR) characteristics of an 850-nm optoelectronic integrated circuit (OEIC) receiver fabricated with standard 0.25- $\mu$ m SiGe bipolar complementary metal-oxide-semiconductor (BiCMOS) technology. The OEIC receiver is composed of a Si avalanche photodetector (APD) and BiCMOS analog circuits including a transimpedance amplifier with DC-balanced buffer, a tunable equalizer, a limiting amplifier, and an output buffer with 50- $\Omega$  loads. We measure APD SNR characteristics dependence on the reverse bias voltage as well as BiCMOS circuit noise characteristics. From these, we determine the SNR characteristics of the entire OEIC receiver, and finally, the results are verified with bit-error rate measurement.

©2014 Optical Society of America

**OCIS codes:** (250.1345) Avalanche photodiodes (APDs); (250.3140) Integrated optoelectronic circuits; (250.0250) Optoelectronics.

# **References and links**

- F.-P. Chou, G.-Y. Chen, C.-W. Wang, Y.-C. Liu, W.-K. Huang, and Y.-M. Hsin, "Silicon photodiodes in standard CMOS technology," IEEE J. Sel. Top. Quantum Electron. 17(3), 730–740 (2011).

- 2. H. Zimmermann, Integrated silicon optoelectronics, 2nd ed. (Springer, 2010).

- 3. A. C. Carusone, H. Yasotharan, and T. Kao, "CMOS technology scaling considerations for multi-gbps optical receivers with integrated photodetectors," IEEE J. Solid State Circuits **46**(8), 1832–1842 (2011).

- Y. Dong and K. W. Martin, "A high-speed fully-integrated POF receiver with large-area photo detectors in 65 nm CMOS," IEEE J. Solid State Circuits 47(9), 2080–2092 (2012).

- T. K. Woodward and A. V. Krishnamoorthy, "1-Gb/s integrated optical detectors and receivers in commercial CMOS technologies," IEEE J. Sel. Top. Quantum Electron. 5(2), 146–156 (1999).

H.-S. Kang, M.-J. Lee, and W.-Y. Choi, "Si avalanche photodetectors fabricated in standard complementary

- H.-S. Kang, M.-J. Lee, and W.-Y. Choi, "Si avalanche photodetectors fabricated in standard complementary metal-oxide-semiconductor process," Appl. Phys. Lett. 90(15), 151118 (2007).

- M.-J. Lee and W.-Y. Choi, "A silicon avalanche photodetector fabricated with standard CMOS technology with over 1 THz gain-bandwidth product," Opt. Express 18(23), 24189–24194 (2010).

- J.-S. Youn, M.-J. Lee, K.-Y. Park, and W.-Y. Choi, "10-Gb/s 850-nm CMOS OEIC receiver with a silicon avalanche photodetector," IEEE J. Quantum Electron. 48(2), 229–236 (2012).

- J.-S. Youn, M.-J. Lee, K.-Y. Park, H. Rücker, and W.-Y. Choi, "An integrated 12.5-Gb/s optoelectronic receiver with a silicon avalanche photodetector in standard SiGe BiCMOS technology," Opt. Express 20(27), 28153– 28162 (2012).

- B. Heinemann, R. Barth, D. Knoll, H. Rücker, B. Tillack, and W. Winkler, "High-performance BiCMOS technologies without epitaxially-buried subcollectors and deep trenches," Semicond. Sci. Technol. 22(1), S153– S157 (2007).

- M.-J. Lee, H.-S. Kang, and W.-Y. Choi, "Equivalent circuit model for Si avalanche photodetectors fabricated in standard CMOS process," IEEE Electron Device Lett. 29(10), 1115–1117 (2008).

- 12. P. P. Webb, R. J. McIntyre, and J. Conradi, "Properties of avalanche photodiode," RCA Rev. **35**, 234–278 (1974).

- 13. E. Säckinger, Broadband Circuits for Optical Fiber Communication (Wiley, 2005).

- 14. Philips Semiconductors Product Specification (SA5212A) (Philips Semiconductors, 1998).

- C.-F. Liao and S.-I. Liu, "40 Gb/s transimpedance-AGC amplifier and CDR circuit for broadband data receivers in 90 nm CMOS," IEEE J. Solid State Circuits 43(3), 642–655 (2008).

- 16. P. Muller and Y. Leblebici, *CMOS Multichannel Single-Chip Receivers for Multi-Gigabit Optical Data Communications* (Springer, 2007).

#### 1. Introduction

There are active research activities for realizing high-performance optoelectronic integrated circuit (OEIC) receivers for 850-nm short-distance optical interconnect applications. For these applications, the use of standard Si technology is very attractive since it can provide cost-effective solutions with high-volume manufacturability [1]. Moreover, monolithic integration of Si photodetectors (PDs) and Si electronic circuits can provide performance enhancement by eliminating undesired parasitic inductances and capacitances [2–4].

However, PDs realized with standard Si technology suffer from low photo-detection efficiency and/or limited photodetection bandwidth. This is due to narrow depletion regions allowed with standard Si processing technology and consequential slow diffusive transport of photo-carriers generated in charge neutral regions [5]. As a way of overcoming these problems, we have investigated Si avalanche photodetectors (APDs) based on P<sup>+</sup>/N-well [6] or N<sup>+</sup>/P-well [7] junction. These APDs provide high responsivity as well as large photodetection bandwidth. In particular, the APD reported in [7] achieved gain-bandwidth product over 1 THz, the largest ever reported for Si APDs. We also realized high-performance Si OEIC receivers in which the APD is monolithically integrated with Si electronics [8], [9].

In these OEIC receivers, the bit-error rate (BER) performance has strong dependence on the APD reverse bias voltage ( $V_R$ ) [8], [9]. In this paper, we investigate signal-to-noise ratio (SNR) characteristics of our OEIC receiver in an attempt to have clear understanding of this dependence and establish design guides for optimized OEIC receivers. Specifically, we measure APD SNR dependence on  $V_R$  and electronic circuit noises and, from these, SNR characteristics of the entire OEIC receiver are determined. Finally, the results are verified with BER measurements.

#### 2. SiGe BiCMOS OEIC receiver

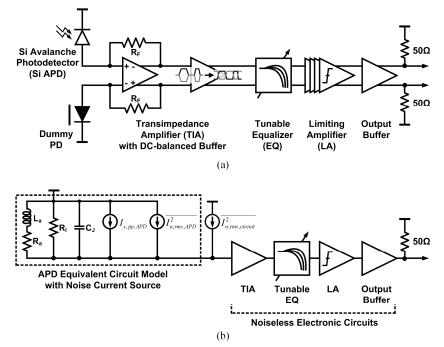

Fig. 1. Simplified block diagram of (a) the fabricated OEIC receiver [9] (b) OEIC receiver for SNR investigation.

Figure 1(a) shows a simplified block diagram of our OEIC receiver. It is fabricated with IHP's standard 0.25-µm SiGe bipolar complementary metal-oxide-semiconductor (BiCMOS)

technology [10], and composed of a Si APD along with a dummy PD, a transimpedance amplifier (TIA) with DC-balanced buffer, a tunable equalizer, a limiting amplifier, and an output buffer. The APD is realized P<sup>+</sup>/N-well junction surrounded by shallow trench isolation. The optical window is about 10  $\mu$ m × 10  $\mu$ m. The dummy PD provides TIA input symmetry. The TIA is designed in shunt-feedback configuration to achieve low-noise characteristics, and a DC-balanced buffer is used for fully differential signaling. The equalizer compensates bandwidth limitation of APD and TIA, and its high-frequency boosting gain can be tuned with a capacitor array. The limiting amplifier is composed of four-stage differential amplifier having emitter degeneration, and the output buffer is used for driving 50- $\Omega$  loads. The power consumption excluding the output buffer is about 59 mW with 2.5-V supply voltage. It can achieve 12.5-Gb/s operation with BER of 10<sup>-12</sup>. Further details for this OEIC receiver can be found in [9].

#### 3. Signal-to-noise ratio (SNR) determination

Figure 1(b) illustrates a simplified block diagram of our OEIC receiver used for SNR investigation. An APD equivalent circuit model [11] including a noise current source is shown, and the electronic circuit noise is modeled with an input-referred noise current source. Then, SNRs for APD (SNR<sub>APD</sub>) and OEIC receiver (SNR<sub>OEIC</sub>) can be described as:

$$SNR_{APD}(V_{R}) = \frac{I_{s,pp,APD}(V_{R})}{\sqrt{I_{n,rms,APD}^{2}(V_{R})}},$$

(1)

$$SNR_{OEIC}(V_R) = \frac{I_{s,pp,APD}(V_R)}{\sqrt{I_{n,rms,APD}^2(V_R) + I_{n,rms,circuit}^2}},$$

(2)

where  $I_{s,pp,APD}$  and  $I_{n,rms,APD}$  represent peak-to-peak signal current and root mean square (rms) noise current of APD, respectively, both of which depend on V<sub>R</sub>.  $I_{n,rms,circuit}$  represents rms input-referred noise current of the electronic circuits. By measuring  $I_{s,pp,APD}$ ,  $I_{n,rms,APD}$ , and  $I_{n,rms,circuit}$  at different V<sub>R</sub> values, numerical values for SNR<sub>APD</sub> and SNR<sub>OEIC</sub> can be determined.

3.1 Si avalanche photodetector (APD)

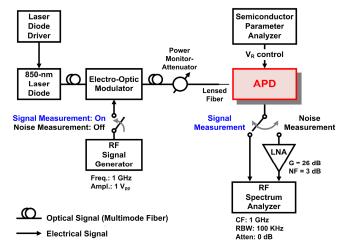

Fig. 2. Experimental setups for APD signal and noise measurement.

For measuring  $I_{s,pp,APD}$  and  $I_{n,rms,APD}$ , the setup shown in Fig. 2 is used. For signal measurement, 850-nm light from a laser diode is modulated at 1 GHz by an external electro-

optic modulator. 1-GHz modulation is used because it is experimentally found that APD photodetection frequency response is very flat around this frequency resulting in more reliable experimental results. The modulated light is transmitted through multimode fiber, and injected into the APD through a lensed fiber. The signal power is determined by measuring APD output signal at 1 GHz with a spectrum analyzer having  $50-\Omega$  load.

The noise power spectral density at 1 GHz is measured using the spectrum analyzer with unmodulated optical input as shown in Fig. 2. Since the resulting noise level is less than the resolution limit of our spectrum analyzer, APD output signal is amplified with a commercial low-noise amplifier (LNA) having 26-dB gain and 3-dB noise figure. APD noise power spectral density is determined by calibrating these results with LNA gain and noise figure. Since APD noise power can be obtained by multiplying the measured noise power spectral density at 1 GHz with the equivalent noise bandwidth determined from the measured photodetection frequency response of our APD [9]. Then, the measured APD signal and noise power are converted into  $I_{s,pp,APD}$  and  $I_{n,rms,APD}$ , respectively. For this, the influence of APD output impedance can be ignored since it is much larger than 50- $\Omega$  load provided by the spectrum analyzer.

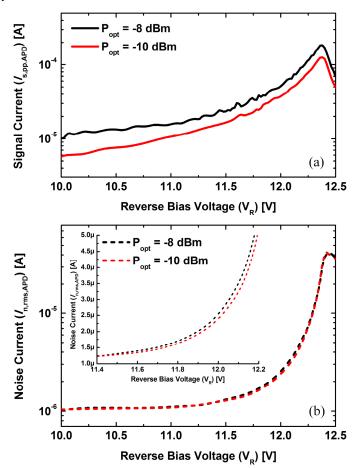

Fig. 3. Measured APD (a) signal and (b) noise characteristics as a function of reverse bias voltage  $(V_R)$ .

Figure 3 shows measured  $I_{s,pp,APD}$  and  $I_{n,rms,APD}$  as a function of  $V_R$  at two different incident optical powers ( $P_{opt}$ ) of -8 and -10 dBm. With increasing  $V_R$ ,  $I_{s,pp,APD}$  increases due to avalanche gain, reaching the maximum at  $V_R$  of about 12.4 V. As expected,  $I_{s,pp,APD}$  is larger

for larger  $P_{opt}$ . The maximum responsivity of our APD is about 1.4 A/W, which is much lower compared to conventional 850-nm APDs. This is due to the fact that our APD is realized with the standard Si technology which does not allow optimal APD device structure.  $I_{n,rms,APD}$  also increases with increasing  $V_R$  due to increasing avalanche noise.  $I_{n,rms,APD}$  is slightly larger for larger  $P_{opt}$  as shown in the inset of Fig. 3(b). Both noise currents are nearly the same for  $V_R$ below about 11.5 V since the thermal noise is the dominant noise for APD in the range. With increasing  $V_R$ , the shot noise becomes more pronounced, and consequently, larger  $P_{opt}$ produces larger  $I_{n,rms,APD}$  [13].

#### 3.2 Electronic circuits

For measuring  $I_{n,rms,circuit}$ , a receiver IC without on-chip APD fabricated within the same run as our OEIC receiver is used. For noise measurement, the input node is left open, and one of two differential outputs is terminated with 50- $\Omega$  load, and the other is connected to a spectrum analyzer [14]. Equalizer boosting gain is set at it minimum value of 4 dB to minimize the effects of noise boosting. The noise frequency characteristics are measured from 100 MHz to 10 GHz, and the effect of electrical cable loss is compensated. Although noise characteristics can be affected by RF pads used for the measurement purpose, their influence is not significant since the pad capacitance is relatively small. The output noise power is converted into output noise voltage, and then, the output noise voltage is referred to the input node by dividing the resulting output noise voltage with the measured transimpedance frequency response of the receiver IC.

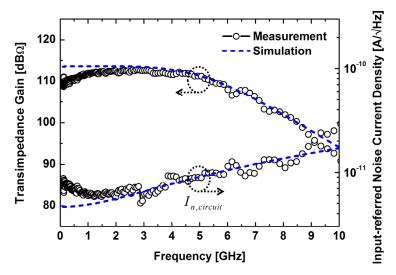

Fig. 4. Measured and simulated signal and noise frequency characteristics of electronic circuits with minimum equalization.

Figure 4 shows the resulting input-referred noise current density ( $i_{n,circuit}$ ) as well as the measured transimpedance frequency response of the receiver IC.  $I_{n,rms,circuit}$  can be determined using below equation [15]:

$$\overline{I_{n,rms,circuit}^{2}} = \left[\int_{100MHz}^{BWs} \overline{i_{n,circuit}^{2}} df\right] \cdot \frac{BW_{n}}{BW_{s}},$$

(3)

where  $BW_s$  and  $BW_n$  is the signal and equivalent noise bandwidth of the receiver IC, respectively. The resulting  $I_{n,rms,circuit}$  of our electronic circuits is about 0.83  $\mu$ A<sub>rms</sub>. Figure 4 also shows our measurement results agree well with the simulation results. For both transimpedance and noise simulation, Spectre simulator in Cadence is used.

## 3.3 OEIC receiver

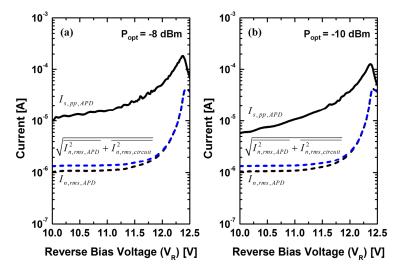

Fig. 5. Measured APD signal and noise current with and without electronic circuit noise at incident optical power ( $P_{opt}$ ) of (a) –8 and (b) –10 dBm, respectively.

Figure 5 shows APD signal current along with two different noise currents, one for APD alone and the other for the total OEIC receiver, at different bias voltages with two different  $P_{opt}$  levels of -8 and -10 dBm. It can be observed that the total OEIC receiver noise is dominated by the APD noise when  $V_R$  approaches the breakdown voltage.

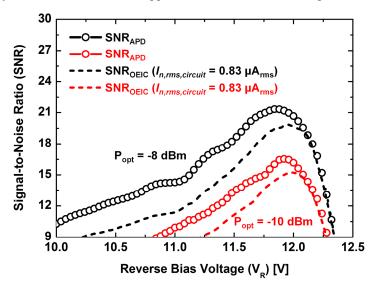

Fig. 6. Estimated SNR<sub>APD</sub> and SNR<sub>OEIC</sub> as a function of  $V_R$  at incident optical power ( $P_{opt}$ ) of -8 and -10 dBm, respectively.

With these measurement results, numerical values for  $SNR_{APD}$  and  $SNR_{OEIC}$  can be determined using Eq. (1) and Eq. (2). Figure 6 shows the resulting  $SNR_{APD}$  and  $SNR_{OEIC}$  at different bias voltages.  $SNR_{APD}$  is the highest for  $V_R$  of about 11.9 V, which is less than  $V_R$  of 12.4 V that gives the maximum APD signal current shown in Fig. 3(a). For  $V_R$  below 11.9 V,  $SNR_{APD}$  is degraded because APD does not have sufficient avalanche gain. For  $V_R$  above 11.9 V, there is too much APD noise. The short-dashed lines in Fig. 6 show the estimated

$SNR_{OEIC}$ . It has the highest value for  $V_R$  of about 12.0 V. The optimal  $V_R$  for  $SNR_{OEIC}$  is slightly higher than that for  $SNR_{APD}$  since APD needs to provide slightly larger gain due to the circuit noise.

#### 4. Confirmation by bit-error rate measurement

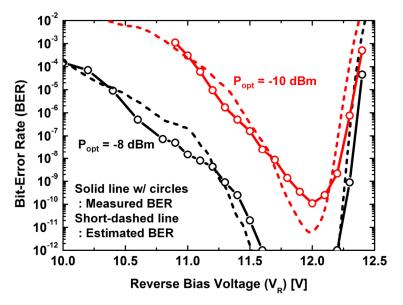

Fig. 7. Measured and estimated BER as a function of  $V_R$  at incident optical power ( $P_{opt}$ ) of -8 and -10 dBm, respectively.

To verify the accuracy of the estimated SNR<sub>OEIC</sub>, BER performance of our OEIC receiver is measured at different reverse bias voltages, and the results are compared with the BER determined from SNR<sub>OEIC</sub>. For this measurement, equalizer boosting gain is minimized to alleviate any noise boosting and signal distortion due to over-equalized frequency response. In addition, the data rate is set below the OEIC receiver 3-dB bandwidth of 7.5 GHz [9] to avoid any BER degradation due to inter-symbol interference caused by limited OEIC receiver bandwidth. Figure 7 shows the measured BER when 6-Gb/s broadband optical data are detected by our OEIC receiver at  $P_{opt}$  of -8 and -10 dBm, respectively. The short-dashed lines in Fig. 7 show the estimated BER derived with the following equation:

$$BER = \frac{1}{2} \cdot erfc \left( \frac{\alpha \cdot SNR_{OEIC}}{2\sqrt{2}} \right).$$

(4)

In Eq. (4),  $\alpha$  represents signal penalties due to fiber dispersion, transmitter bandwidth, and experimental loss [16]. In our case,  $\alpha$  is estimated to be 0.88 by fitting measured data to Eq. (4) with the minimum squared error. As shown in Fig. 7, for P<sub>opt</sub> of -10 dBm, the best BER performance is achieved at V<sub>R</sub> of about 12.0 V, corresponding to V<sub>R</sub> having the highest SNR<sub>OEIC</sub> as shown in Fig. 6. For P<sub>opt</sub> of -8 dBm, the measured BER is equal to or less than  $10^{-12}$  for V<sub>R</sub> of from 11.6 V to 12.2 V. Although not shown in Fig. 7, the fitting curve has the minimum BER of about  $10^{-19}$  at V<sub>R</sub> of about 12.0 V, which corresponds to the V<sub>R</sub> having the highest SNR<sub>OEIC</sub> for P<sub>opt</sub> of -8 dBm.

## 5. Conclusion

We investigate SNR characteristics of an OEIC receiver fabricated with standard 0.25- $\mu$ m SiGe BiCMOS technology. APD signal and noise characteristics are determined at different V<sub>R</sub> values, and electronic circuit noise is measured. With measurement results, SNR

characteristics of our OEIC receiver are determined, and the results are verified with BER measurement.

# Acknowledgments

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST) [2012R1A2A1A01009233]. The authors would like to thank Minsu Ko and Jeong-Min Lee in High-Speed Circuits and Systems Laboratory, Yonsei University, for many helpful discussions. The authors are also very thankful to IC Design Education Center (IDEC) for EDA software support.